各位亲爱的网友们,大家好!

在2026年国际消费电子展(CES)上,AMD展示了即将推出的Venice系列服务器CPU和MI400系列数据中心加速器。AMD曾在2025年6月的“Advancing AI”活动上介绍过Venice和MI400系列的规格,但此次是AMD首次公开展示这两个产品线的芯片。

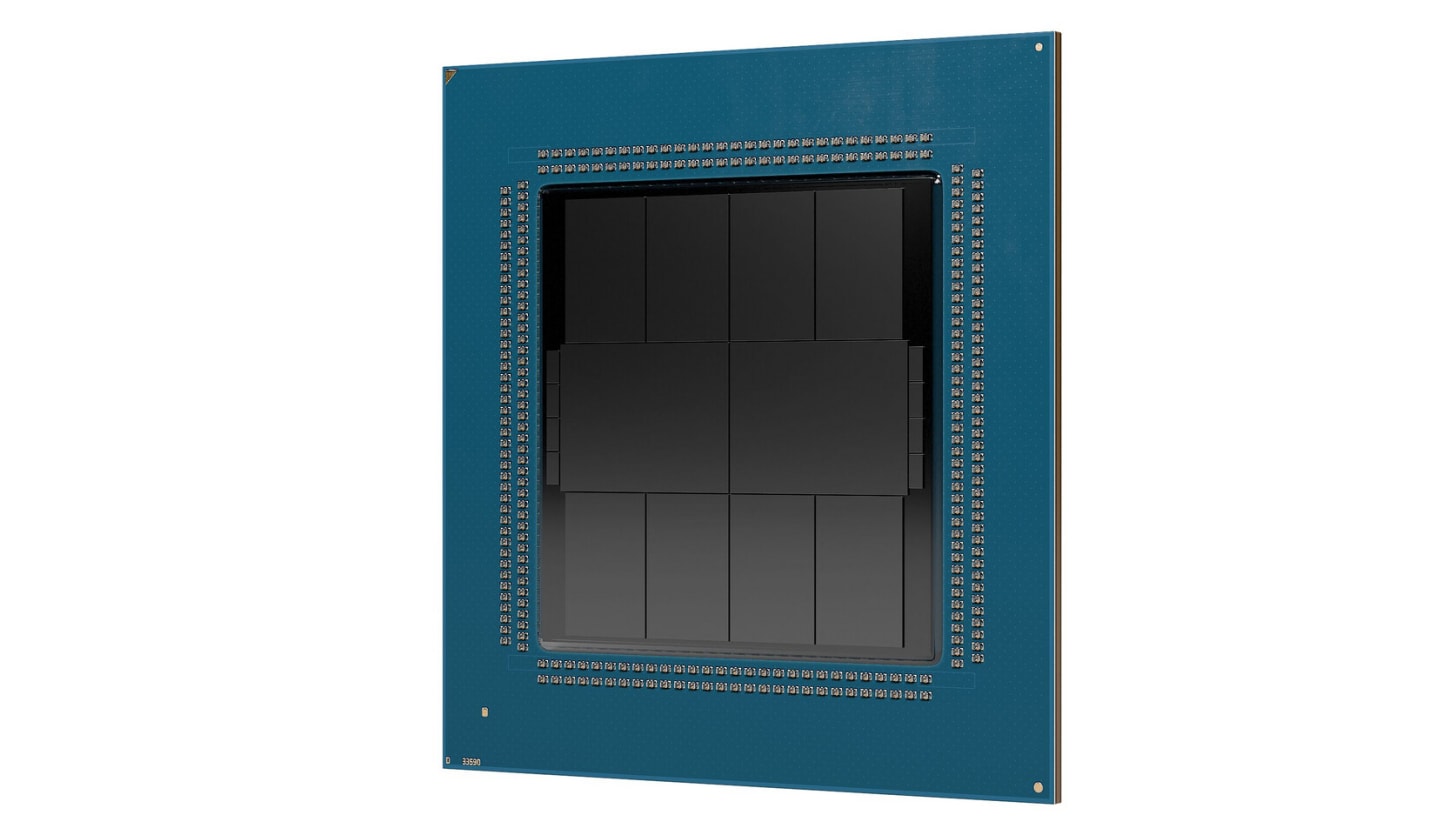

首先,Venice 处理器最显著的变化在于其 CCD 与 I/O 芯片的封装方式有所不同。AMD 自 EPYC Rome 以来一直使用封装的有机基板来连接 CCD 和 I/O 芯片,而 Venice 似乎采用了一种更先进的封装方式,类似于 Strix Halo 或 MI250X。另一个变化是,Venice 似乎配备了两个 I/O 芯片,而不是之前 EPYC CPU 的单个 I/O 芯片。

Venice 芯片包含 8 个 CCD,每个 CCD 有 32 个核心,因此每个 Venice 封装最多可容纳 256 个核心。对每个芯片进行测量后发现,每个 CCD 的 N2 硅面积约为 165 平方毫米。如果 AMD 坚持每个核心配备 4MB 的 L3 缓存,那么每个 CCD 就包含 32 个 Zen 6 核心和 128MB 的 L3 缓存,以及用于 CCD 与 I/O 芯片通信的芯片间接口。每个 CCD 的面积约为 165 平方毫米,这意味着每个 Zen 6 核心加上 4MB 的 L3 缓存大约占5平方毫米,这与 Zen 5 核心加上 4MB L3 缓存后 N3 芯片的面积(约 5.34 平方毫米)相近。

接下来看I/O芯片,每个芯片的面积约为353平方毫米,总共超过700平方毫米的硅片用于I/O芯片。这比之前的EPYC CPU的I/O芯片面积(约400平方毫米)有了显著提升。这两个I/O芯片似乎采用了某种类似于CCD的先进封装技术。在I/O芯片旁边,封装两侧各有4个小芯片,共8个,它们可能是结构硅片或深沟槽电容芯片,旨在改善CCD和I/O芯片的供电。

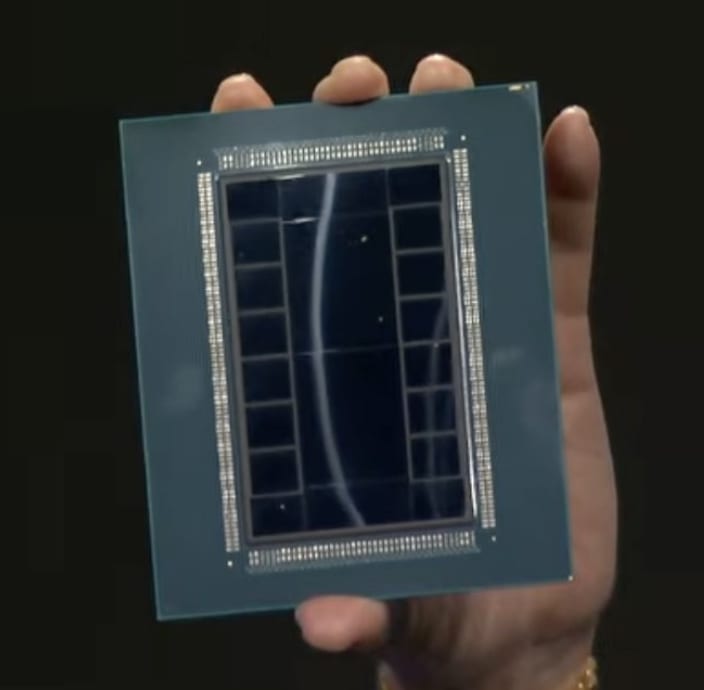

离开威尼斯,我们来看看MI400加速器。这款芯片封装尺寸巨大,包含12颗HBM4显存芯片和“12颗2纳米和3纳米制程的计算和I/O芯片”。它似乎和MI350一样,有两个基础芯片。但与MI350不同的是,MI400的基础芯片顶部和底部似乎还有两个额外的芯片。这两个额外的芯片很可能用于封装外I/O,例如PCIe、UALink等。

通过计算基础芯片和I/O芯片的面积,两个基础芯片的面积约为747平方毫米,而封装外的I/O芯片的面积约为220平方毫米。至于计算芯片,虽然封装方式使得不同计算芯片之间无法直接区分,但很可能共有8个计算芯片,每个基础芯片上集成4个计算芯片。因此,虽然我们无法确定计算芯片的确切面积,但其最大面积约为180平方毫米。计算芯片组的面积可能在140平方毫米到160平方毫米之间,但这只是最佳估计,还需要进一步验证。

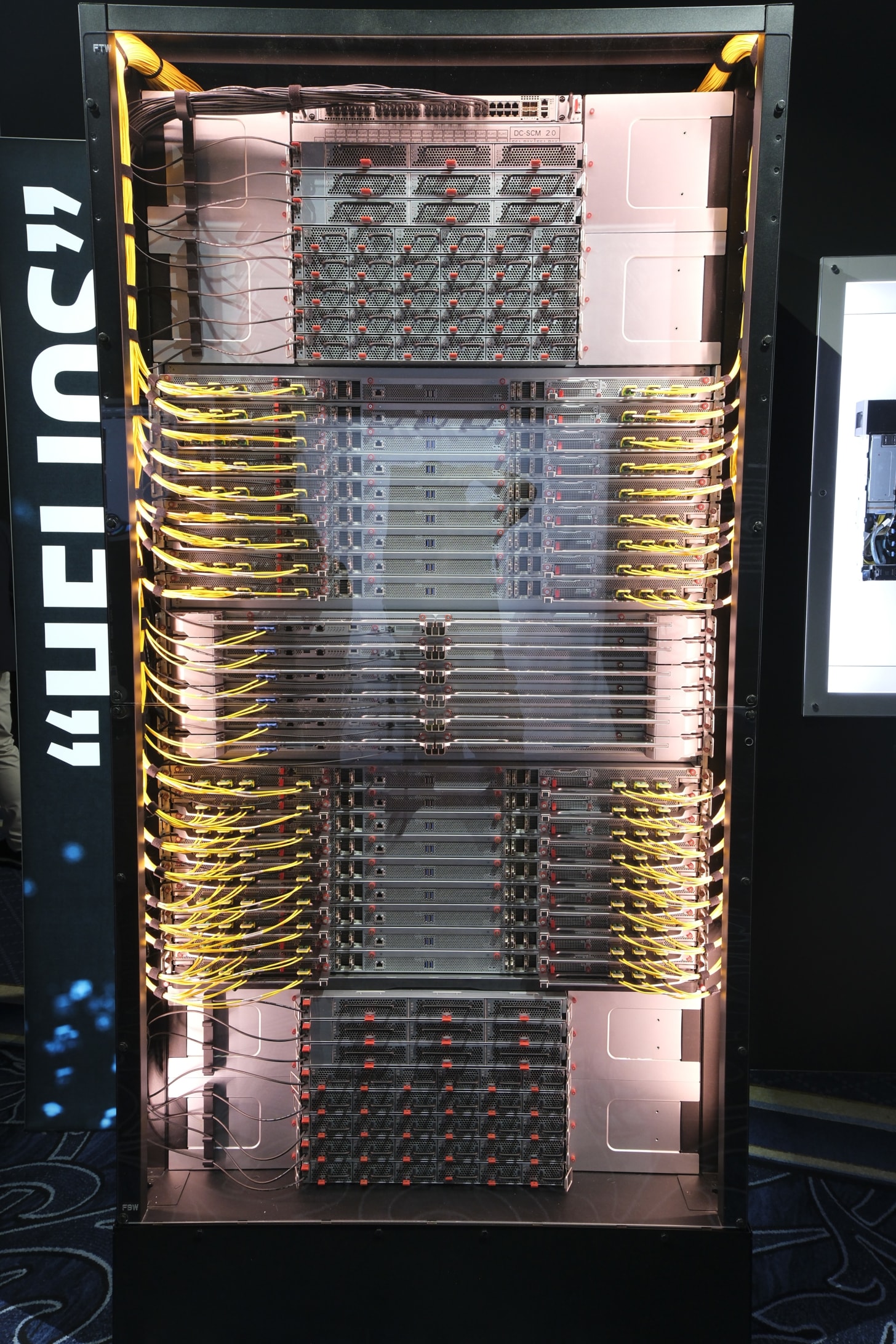

MI455X 和 Venice 是两款将用于 AMD Helios AI Rack 的 SoC,但它们并非 AMD 在 CES 上发布的唯一 Zen 6 和 MI400 系列新产品。AMD 还宣布 MI400 系列将新增第三款产品 MI440X,与 MI430X 和 MI455X 共同组成该系列。MI440X 专为 8 路 UBB 机箱设计,可直接替代 MI300/350 系列。

AMD 还发布了 Venice-X,它很可能是 Venice 的 V-Cache 版本。这很有意思,因为 AMD 不仅跳过了 Turin-X,而且如果 Venice-X 真的有 256 核心版本,那么这将是高核心数 CCD 首次能够支持 V-Cache 芯片。如果 AMD 保持基础芯片缓存与 V-Cache 芯片缓存的比例不变,那么每个 32 核心 CCD 将拥有高达 384MB 的 L3 缓存,整个芯片的 L3 缓存总量可达 3GB。

Venice 和 MI400 系列都将于今年晚些时候发布,我迫不及待地想了解这两款 SoC 的底层架构。

如果你喜欢这些内容,可以考虑前往Patreon或PayPal给 Chips and Cheese 捐赠一些钱,也可以考虑加入Discord 。

原文: https://chipsandcheese.com/p/ces-2026-taking-the-lids-off-amds