为了将像CPU这样的微型集成电路世界与外界连接起来,必须建立许多物理连接。虽然这看似简单,但这些I/O焊盘会对芯片的功能和完整性构成重大风险,例如静电放电 (ESD)、一种称为闩锁的短路以及噪声等因素造成的亚稳态。保护精密的ASIC免受残酷的外界影响是I/O电路的任务, [Ken Shirriff]最近深入研究了英特尔386 CPU中的I/O电路。

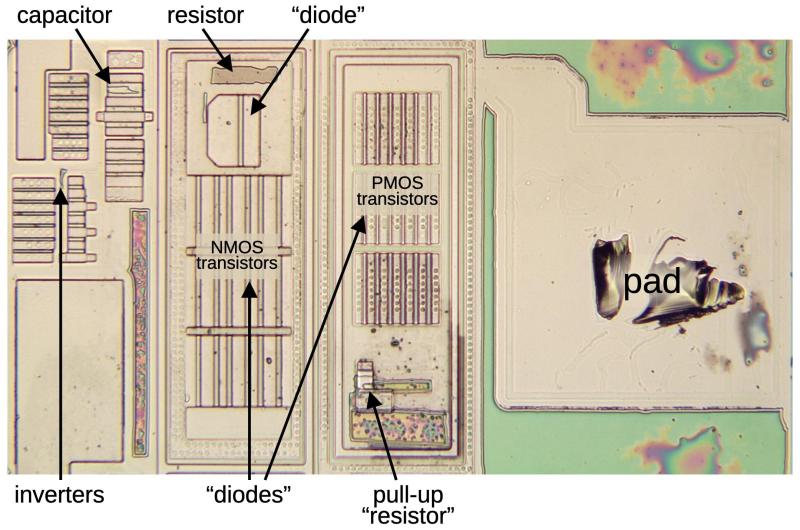

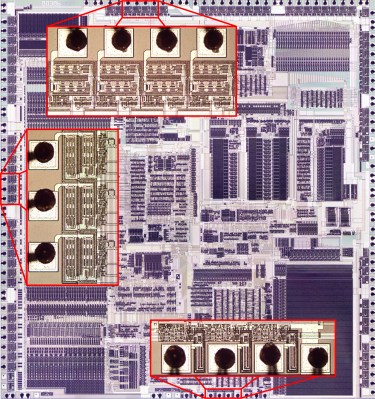

386芯片,部分焊盘电路放大图。(图片来源:Ken Shirriff)

386芯片,部分焊盘电路放大图。(图片来源:Ken Shirriff)

386 总共有 141 个 I/O 焊盘,每个焊盘都通过一根精致的金线连接到封装上的引脚。ESD 是潜在风险中的第一大风险,因为高压浪涌可能会在电路上炸出一个洞。上面的芯片照片中可以看到保护电路,其中包括钳位二极管、限流电阻和第三个二极管。

闩锁效应是第二个主要问题,它是由PMOS晶体管和NMOS晶体管下方意外产生的寄生结构引起的。这些寄生晶体管通常处于非激活状态,但如果被激活,则会引起闩锁效应,在最好的情况下会导致瞬时故障,而在最坏的情况下,大电流会熔化芯片的一部分。

为了防止输入/输出引脚触发闩锁效应,386 处理器采用了“保护环”来阻断不必要的电流。最后,还有亚稳态效应,顾名思义,它并不一定有害,但会严重干扰芯片的运行,因为芯片需要的是干净的二进制信号。386 处理器上每个输入/输出引脚使用两个触发器,主要是为了解决这个问题。

尽管以今天的标准来看,1985 年生产的 386 电路非常不成熟,但它仍然无法抵御这些外部影响,这清楚地表明这些保护措施对于当今特征尺寸小得多的 ASIC 来说是多么重要。

原文: https://hackaday.com/2025/08/21/how-intels-386-protects-itself-from-esd-latch-up-and-metastability/